# Understanding Switch Linearity Performance

## **Application Note 58**

## **Summary**

This application note demonstrates the need to know more than just basic RF performance metrics when determining how a part will perform in an actual system. Using WLAN error vector magnitude (EVM) requirements as a test case, it will be shown that simply knowing a part has sufficient headroom to the power requirement does not guarantee adequate linearity response in the actual system.

## Introduction

As data communication requirements increase, the systems designed to carry the data require higher levels of performance. For RF systems this means increasing the signal bandwidth and increasing the modulation density. In the WLAN evolution from 802.11a to 802.11b to 802.11g to 802.11n to 802.11ac, the bandwidth has increased from 10 MHz to >80 MHz, with the modulation increasing from 64 quadrature amplitude modulation (QAM) to 256 QAM. In these systems it is the quality of the QAM constellation that is the core factor in determining system performance limits. EVM is the measure of error in the position of each symbol in the constellation map. The constellation map is a diagrammatic representation of the data to modulation map for a QAM modulation. The EVM figure has no information other than the size of the error.

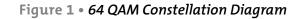

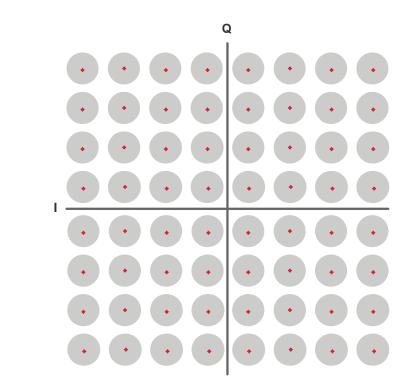

**Figure 1** and **Figure 2** show the constellation diagram for two different forms of QAM: 64 and 256. These figures refer to the number of points on the constellation, i.e., the number of distinct states that can exist. The shadow areas around each point represent an estimation of the allowable constellation error.

While higher order modulation rates (i.e., 256 QAM) offer much faster data rates and higher levels of spectral efficiency for the radio communications system, they are considerably less resistant to noise and interference. The maximum allowed error is less for 256 QAM compared to 64 QAM.

<sup>©2016,</sup> Peregrine Semiconductor Corporation. All rights reserved. • Headquarters: 9380 Carroll Park Drive, San Diego, CA, 92121

## Application Note 58 Understanding Switch Linearity

Figure 2 • 256 QAM Constellation Diagram

As the order of the modulation increases, so does the number of symbols on the QAM constellation diagram. With the increased number of symbols, the symbol density increases and the separation between symbols decreases. Therefore, the max allowed constellation error is much smaller for 256 QAM compared to 64 QAM.

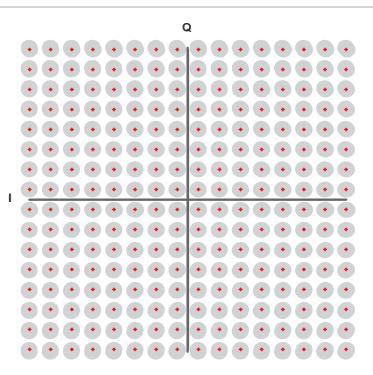

**Figure 3** shows the relationship between the symbol vector and the error vector. The resulting error vector is the difference between the actual measured and ideal symbol vectors.

#### Figure 3 • Relationship Between Symbol Vector and Error Vector

As the data throughput increases, the constellation density increases and therefore the maximum allowed EVM decreases to ensure the constellation points remain distinct without overlapping.

EVM is a measure of the system performance in the presence of impairments. But the figure alone does not identify the source of the distortion. The error signals measured and quantified by EVM metric encompass all the sources of error that are introduced during the modulation and transmission process. It is often difficult to predict EVM performance from any of the usual linearity quality factors such as P1dB or IP3. This increasingly tight system of EVM limits are restricted by the low power system performance such as modulator DC offset or modulator phase accuracy. At the front end, the power amplifier's EVM performance may be dominated by the AM–AM or AM–PM performance rather than P1dB or IP3 linearity figures.

As a result, it is often necessary to use direct EVM measurements rather than other quality figures to undertake system performance analysis.

### Example of EVM for a 5 GHz PA Under 64 QAM 802.11a and 256 QAM 802.11ac Signals

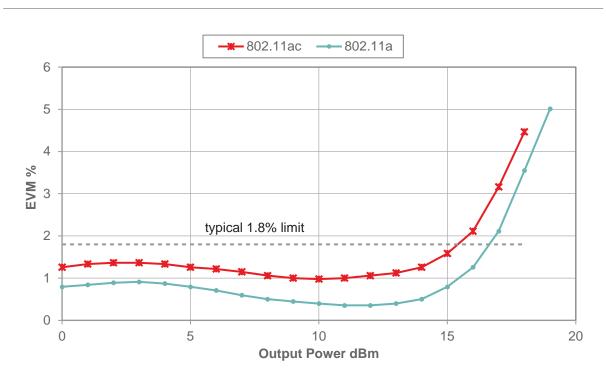

**Figure 4** shows the measurement of EVM for a 5 GHz PA under 64 QAM 802.11a and 256 QAM 802.11ac signals. Notice the EVM result for 802.11ac signal is higher than the EVM result for 802.11a signal, even though this is the same PA under the same temperature, voltage and duty cycle measurement conditions.

It is not the purpose of this application note to define the cause of the EVM degradation between the systems. Assuming the power amplifier AM–AM, AM–PM and P1dB remain constant between the measurements, the dominant factor is likely to be the measured signal bandwidth. However, the purpose of this note is only to show that the 802.11ac performance is generally worse than the 802.11a performance. It also shows the tighter EVM requirement for 802.11ac. This emphasizes the requirement to know the measured EVM rather than any EVM performance assumed or interpolated from the P1dB or IP3 figures in the datasheet.

Figure 4 • 5 GHz WLAN PA EVM

By comparison of the EVM curves, the margin of the PA EVM to the required 802.11ac limit is very small over most of the power curve, even at lower powers. The 802.11 requirement has become more difficult while the corresponding PA performance has dropped, possibly due to the increased bandwidth of operation. In some cases the margin of EVM to the specification is <0.5%. This performance is not unusual and is not restricted to this example. It occurs in most PAs. The effort needed to design a PA that meets the 802.11ac EVM requirements across the whole of the 5 GHz band while being flat in gain across an 80 MHz channel and still being as efficient as possible should not be underestimated. As the output power requirement of the system increases from domestic access point to commercial enterprise systems, the PA EVM performance requirements will become even more critical.

#### Peregrine's PE42424 UltraCMOS® SPDT RF Switch

Peregrine's switches are manufactured on Peregrine's UltraCMOS process, which exhibit an exceptional linearity. This ensures the switch maintains the linearity performance over the whole of the operating input power range.

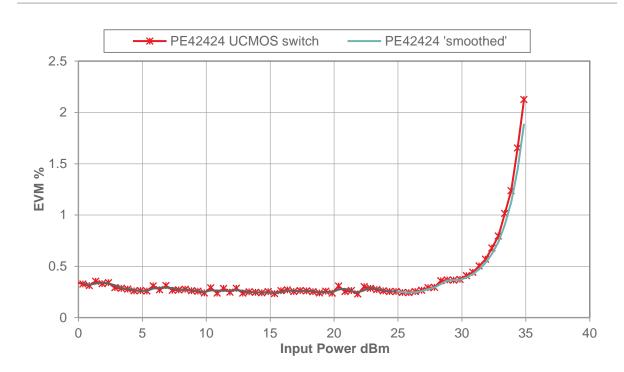

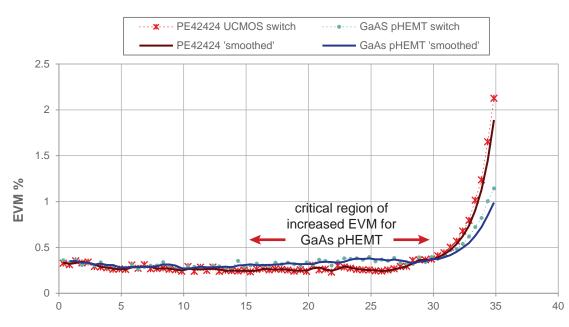

**Figure 5–Figure 7** show that the PE42424 switch does not add any significant EVM to the transmit path for average signal levels of 27 or 28 dBm. Even in the 802.11ac environment the added EVM would be insignificant. In fact, the UltraCMOS process is so linear the switch does not contribute any EVM until the peak of the signal approaches the P1dB of the switch.

Figure 5 • 802.11a EVM

By comparison, other fabrication processes do not exhibit this performance. **Figure 6** shows a GaAs switch with similar P1dB and IP3 figures. Notice the EVM performance starts to degrade before the signal peak hits the P1dB compression point. The EVM for the GaAS device rises to nearly 0.4% well before the signal peak hits the 0.1dB point, whereas the EVM for the UltraCMOS device stays below the measurement noise floor. This could be critical achieving the optimum performance for a high power access point power amplifier (PA) with a 24 dBm power class working with an 802.11ac signal, given the likely minimal margin over the whole input power range.

#### Figure 6 • GaAs Switch

Input Power dBm

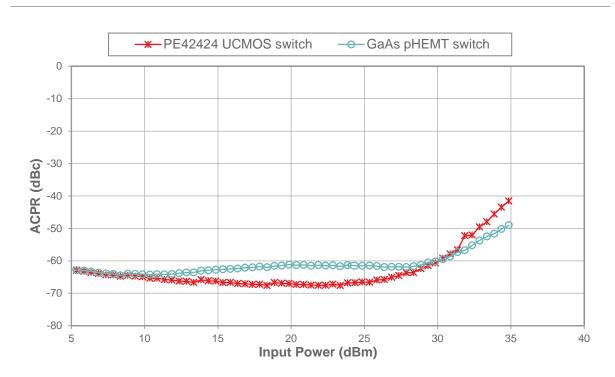

To emphasize this characteristic, the same switches were measured using a 3 GPP ACP signal. This test is much more sensitive to nonlinearity. For the GaAS device the same degradation in performance occurs between 20–27 dBm input power as seen in **Figure 7**, whereas the UltraCMOS device stays below the measurement noise floor.

# Conclusion

UltraCMOS switches are ideal for high linearity applications due to the characteristics of the semiconductor process and existing PSEMI patents. As the input power increases, the switch can maintain the same linearity performance up to the P0.1dB compression point. This high linearity behavior is essential in today's digital communications system where the smallest degradations in linearity can affect the overall system performance.

#### **Sales Contact**

For additional information, contact Sales at sales@psemi.com.

#### Disclaimers

The information in this document is believed to be reliable. However, Peregrine assumes no liability for the use of this information. Use shall be entirely at the user's own risk. No patent rights or licenses to any circuits described in this document are implied or granted to any third party. Peregrine's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Peregrine product could create a situation in which personal injury or death might occur. Peregrine assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

#### **Patent Statement**

Peregrine products are protected under one or more of the following U.S. patents: patents.psemi.com

#### Copyright and Trademark

©2016, Peregrine Semiconductor Corporation. All rights reserved. The Peregrine name, logo, UTSi and UltraCMOS are registered trademarks and HaRP, MultiSwitch and DuNE are trademarks of Peregrine Semiconductor Corp.

www.psemi.com